CXL Types 1, 2, and 3 each offer different memory sharing capabilities suited for various workloads. Type 1 provides fast, low-latency device-level memory access, ideal for accelerators. Type 2 adds shared memory resources, supporting scalable memory expansion. Type 3 creates large memory pools across multiple devices for high-performance tasks. Choosing the right type depends on your performance needs and workload sensitivity. Keep going to uncover detailed differences and how to make the best use of each.

Key Takeaways

- CXL Type 1 provides low-latency, direct memory access for fast device-level memory sharing.

- CXL Type 2 supports shared memory devices and maintains cache coherence with low system latency.

- CXL Type 3 enables large memory pooling across multiple devices for high-capacity, scalable workloads.

- Types differ in bandwidth, latency, and application focus, influencing memory sharing strategies.

- Proper selection depends on workload sensitivity, performance needs, and system topology considerations.

CXL memory sharing hardware

As an affiliate, we earn on qualifying purchases.

As an affiliate, we earn on qualifying purchases.

What Is Compute Express Link (CXL), and Why Does It Matter?

What exactly is Compute Express Link (CXL), and why is it becoming so important in modern computing? CXL is a high-speed interconnect that enables fast communication between CPUs, memory, and accelerators. Its significance grows as quantum networking advances, demanding ultra-low latency and efficient data sharing. CXL’s ability to facilitate seamless memory sharing improves system performance and scalability, making it essential for data centers and AI workloads. Additionally, CXL supports blockchain integration by providing a reliable, high-throughput connection for secure and rapid transaction processing. As digital ecosystems become more complex, CXL’s role in connecting hardware components and enabling innovative applications like quantum networking and blockchain becomes increasingly critical, shaping the future of efficient, connected computing environments. Advanced interconnect technologies continue to evolve, enhancing the capabilities of CXL and its impact on next-generation infrastructure. Furthermore, ongoing developments in high-speed data transfer protocols are expected to further expand CXL’s potential and adoption across various industries. The evolution of hardware connectivity standards is also pivotal in supporting the widespread implementation of CXL in diverse systems.

Photonics Integration And Optical Interconnects For High Speed Computing: Advanced Technologies and Strategies for Next-Generation Data Center Connectivity

As an affiliate, we earn on qualifying purchases.

As an affiliate, we earn on qualifying purchases.

How Do CXL Types 1, 2, and 3 Differ? Key Features at a Glance

Ever wondered how CXL types differ in their capabilities? CXL Type 1 offers direct memory access with high memory bandwidth, ideal for accelerators requiring fast data transfer. Type 2 expands on this by adding support for memory devices directly attached to the host, maintaining low system latency. Type 3 provides the highest flexibility, enabling memory pooling across multiple devices and offering vast memory capacity. While Types 1 and 2 focus on lowering system latency for specific components, Type 3 emphasizes scalable memory sharing, which can introduce slight latency increases but offers greater system-wide memory bandwidth. Understanding these distinctions helps you choose the right CXL type based on your performance needs, balancing memory bandwidth and system latency for best efficiency.

CXL Type 3 memory pooling solutions

As an affiliate, we earn on qualifying purchases.

As an affiliate, we earn on qualifying purchases.

Exploring the CXL Protocol Stack: Layers and Components Explained

The CXL protocol stack is a layered architecture that organizes how data moves between devices, guaranteeing efficient communication and compatibility. It aligns with the memory hierarchy, enabling faster access to data across different levels. The protocol layers include the Physical Layer, which handles electrical signals and physical connections, and the Data Link Layer, managing reliable data transfer. Above this, the Transaction Layer coordinates memory requests, commands, and responses, facilitating seamless communication between hosts and devices. Each layer performs specific functions, working together to optimize data flow and reduce latency. Understanding these protocol layers helps you grasp how CXL supports high-speed memory sharing and accelerates data-intensive workloads. This structure ensures devices operate efficiently within the memory hierarchy, maximizing performance and resource utilization.

Waveshare Jetson Orin NX AI Development Kit for Embedded and Edge Systems, with 16GB Memory Jetson Orin NX Module

This kit includes the Orin NX Module with 16GB memory, no built-in storage module, provides up to 100…

As an affiliate, we earn on qualifying purchases.

As an affiliate, we earn on qualifying purchases.

Understanding CXL Physical Connections and Topology in Hardware

Understanding how CXL physical connections are established is essential for guaranteeing reliable and high-speed communication between devices. The physical topology determines how devices connect within a system, impacting latency and bandwidth. CXL uses specific connector types designed for high data rates and tight integration, such as PCIe-style connectors adapted for CXL protocols. These connector types facilitate direct, high-bandwidth links between CPUs, memory modules, and accelerators, forming a compact, efficient physical topology. Properly selecting and implementing connector types ensures excellent signal integrity and minimizes latency. The physical topology can be point-to-point, switch-based, or a hybrid, depending on system design. By understanding these physical connection principles, you can optimize hardware configurations for maximum performance and reliability.

How CXL Type 1 Enables Fast, Device-Level Memory Sharing

CXL Type 1 connects devices directly to the CPU’s memory subsystem, enabling rapid, low-latency access to memory resources. This direct connection minimizes memory latency, allowing devices like memory expanders or smart NICs to share memory efficiently. Because of its streamlined design, CXL Type 1 guarantees high device interoperability, making it easy for multiple components to communicate seamlessly. You benefit from faster data transfer rates and reduced bottlenecks, which boosts overall system performance. This setup supports real-time data sharing at the device level, essential for demanding workloads such as analytics or artificial intelligence. By providing quick access to memory, CXL Type 1 helps you maximize hardware utilization, ensuring your devices work together smoothly without delays or compatibility issues.

Using CXL Type 2 to Connect Accelerators and Expand Memory Modules

With CXL Type 2, you can connect accelerators more efficiently, boosting overall system performance. It also allows you to expand memory capacity seamlessly, giving you more flexibility for demanding workloads. Managing shared memory resources becomes simpler, helping you optimize resource allocation across devices. This technology paves the way for future-proofing systems, ensuring compatibility with emerging hardware innovations. Additionally, the ability to support shared memory resources enhances system scalability and adaptability for evolving computational needs. By enabling more dynamic resource sharing, CXL Type 2 supports hardware interoperability, facilitating smoother integration of diverse components. Furthermore, this standard promotes system security by enabling controlled access to shared resources. Understanding the fundamentals of memory sharing is essential for leveraging these capabilities effectively.

Connecting Accelerators Efficiently

Connecting accelerators efficiently often hinges on choosing the right interface, and CXL Type 2 excels in this role. It enables direct, high-speed connections that minimize memory latency and maximize power efficiency. To optimize your setup, consider these key points:

- Use CXL Type 2 for low-latency data transfer between accelerators and memory modules.

- Leverage its configurability to allocate resources dynamically, reducing idle power consumption.

- Guarantee proper topology design to minimize unnecessary data hops, improving overall performance.

- Balance bandwidth needs with power efficiency by selecting appropriate link speeds and configurations.

- Understanding the interface’s capabilities ensures you can make the most of its flexible and efficient connectivity options.

Expanding Memory Capacity Seamlessly

Expanding memory capacity seamlessly requires a flexible and high-speed interface that can adapt to growing data demands. CXL Type 2 enables you to connect accelerators directly to memory modules, creating a scalable and unified memory pool. This setup supports memory compression techniques, which optimize available bandwidth and storage, ensuring efficient data handling. Additionally, CXL maintains cache coherence between the host and connected devices, preventing data inconsistencies and reducing latency. By leveraging CXL Type 2, you gain the ability to expand memory capacity without disrupting existing systems, allowing for smoother upgrades and better resource utilization. This approach simplifies managing large datasets and accelerates data processing, making your infrastructure more versatile and future-proof.

Managing Shared Memory Resources

Managing shared memory resources effectively becomes more achievable when you use CXL Type 2 to link accelerators directly to memory modules. This approach streamlines resource allocation and reduces memory fragmentation by providing direct access paths. To optimize your setup, consider these key points:

- Allocate memory dynamically to prevent fragmentation issues.

- Use direct links to minimize latency and improve performance.

- Monitor resource usage regularly to avoid bottlenecks.

- Segment memory pools for different workloads, ensuring efficient distribution.

- Understanding the importance of deep product research helps in selecting the right configurations for your specific needs.

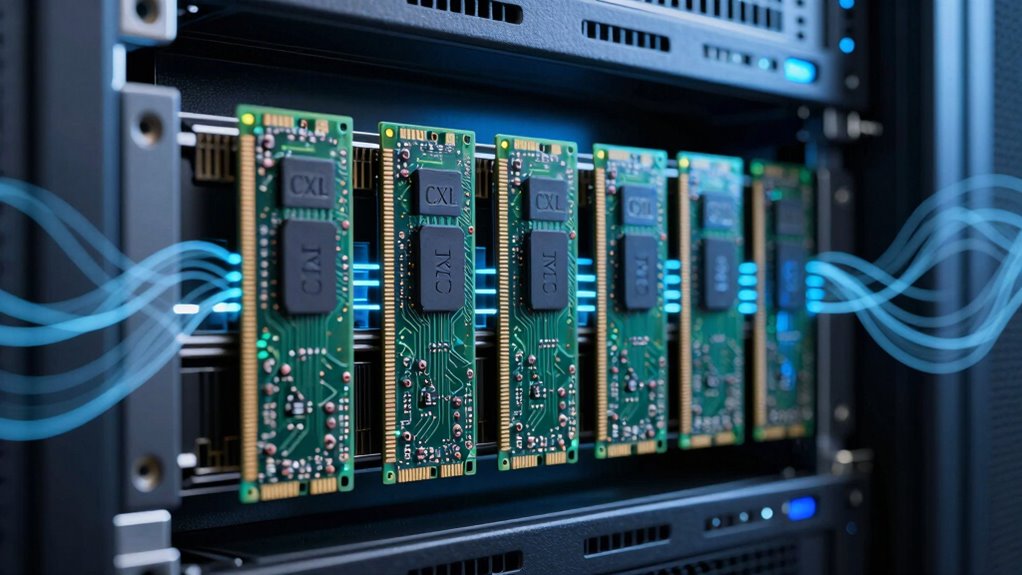

CXL Type 3: Building Large-Scale Memory Pools for Data-Intensive Tasks

CXL Type 3 enables you to create large-scale memory pools that can handle massive data workloads efficiently. With this setup, you can optimize data-intensive tasks and reduce bottlenecks. This approach is essential for boosting performance in demanding computing environments. Additionally, understanding memory sharing mechanisms helps in designing more flexible and scalable systems. Proper implementation of resource allocation strategies further enhances system efficiency and responsiveness, especially when managing vetted wave and wind resources to ensure system stability.

Large-Scale Memory Pooling

Building large-scale memory pools with CXL Type 3 enables data-intensive tasks to access vast amounts of memory seamlessly. This setup allows you to aggregate memory across multiple devices, improving performance for demanding workloads. To optimize this system, consider:

- Managing virtual memory efficiently to prevent bottlenecks.

- Ensuring cache coherence across devices to maintain data consistency.

- Leveraging CXL’s high bandwidth for quick data transfers.

- Implementing robust memory virtualization techniques to maximize utilization.

Optimizing Data-Intensive Tasks

To optimize data-intensive tasks with large-scale memory pools, you need to focus on maximizing the efficiency of data access and transfer. Reducing memory latency is vital, so make certain your system minimizes delays between data requests and responses. CXL Type 3 enables direct access to vast memory pools, but frequent data replication can introduce overhead. To avoid bottlenecks, implement intelligent data placement strategies that limit unnecessary replication and keep data close to processors. Prioritize efficient caching and prefetching techniques to decrease access times. Monitoring and tuning data transfer patterns help identify latency issues, allowing you to optimize throughput. By managing memory latency and reducing redundant data replication, you can substantially improve performance for demanding data-intensive workloads. Incorporating system-level optimizations that align hardware and software configurations can further enhance overall efficiency.

Comparing CXL With PCIE, CCIX, and Other Memory Interconnects

While PCIe has long served as the standard interface for connecting peripherals and memory devices, newer interconnects like CXL and CCIX aim to address PCIe’s limitations by offering higher bandwidth, lower latency, and enhanced memory sharing. These technologies improve the memory hierarchy by enabling direct, coherent access across devices, which boosts performance and simplifies cache coherence management. Key differences include:

- CXL supports cache-coherent memory expansion, unlike traditional PCIe.

- CCIX emphasizes cache-coherent interconnect for accelerators.

- PCIe prioritizes peripheral connectivity over memory sharing.

- CXL and CCIX enable more flexible, scalable memory architectures.

- Memory sharing capabilities are a central focus, allowing systems to utilize resources more efficiently and reduce data bottlenecks. Additionally, the development of these technologies reflects ongoing efforts to integrate memory systems, leading to more unified and efficient data centers.

Together, these interconnects push data centers toward more efficient, unified memory systems, reducing bottlenecks and optimizing cache coherence across devices.

How to Choose the Right CXL Type for Your Data Center or Server

When choosing the right CXL type, you need to contemplate compatibility with your existing hardware and software. Performance and scalability requirements will also influence your decision, ensuring your setup can grow efficiently. By balancing these factors, you can select the most suitable CXL solution for your data center or server. Additionally, understanding art care principles can help optimize the longevity and performance of your hardware investments.

Compatibility Considerations

Choosing the right CXL type for your data center or server depends on understanding your specific performance needs and hardware compatibility. Memory latency impacts how quickly data moves between components, so guarantee your hardware supports the desired CXL type without excessive delays. Compatibility considerations are vital; not all devices or motherboards support every CXL type. To make an informed choice:

- Verify your server’s motherboard and CPU support the CXL version.

- Check if your memory modules are compatible with the CXL type.

- Confirm that your hardware drivers and firmware are updated.

- Consider future upgrades and whether the hardware can adapt to newer CXL standards.

Understanding the hardware specifications ensures your system can fully leverage CXL technology and avoid unexpected bottlenecks.

This guarantees maximum performance while avoiding costly incompatibilities. Prioritizing hardware compatibility helps you leverage CXL’s benefits without unexpected bottlenecks.

Performance and Scalability

Selecting the appropriate CXL type is essential for optimizing your data center’s performance and scaling capacity effectively. CXL Type 1 offers direct memory sharing with high memory bandwidth, ideal for workloads needing rapid data access. Type 2 enhances scalability by combining memory sharing with switches, supporting larger systems while maintaining low latency. Type 3 provides fabric-level interconnectivity, maximizing scalability across multiple devices but with slightly increased latency. Your choice depends on balancing memory bandwidth needs against latency optimization. If you prioritize quick data transfer within a single server, Type 1 is best. For expanding capacity across multiple devices with efficient communication, Type 2 or Type 3 are better suited. Understanding these differences helps guarantee your infrastructure meets performance demands while maintaining scalability. Additionally, choosing the right CXL type can influence your overall system architecture and future growth potential.

Practical Use Cases for CXL Type 1: Device Communication and Management

CXL Type 1 devices play an essential role in streamlining communication and management between various hardware components. They enable direct device-to-host communication, improving efficiency and reducing latency. This setup is especially beneficial for managing virtual memory and maintaining cache coherence across devices. Here are key practical use cases:

- Managing I/O devices efficiently without burdening the CPU.

- Ensuring real-time device status updates for better system control.

- Facilitating seamless device hot-swapping and dynamic configuration.

- Enhancing cache coherence to keep data synchronized between memory and peripherals. Equity Buyers are increasingly leveraging such technologies to optimize infrastructure performance. Ventilation considerations are also important to maintain optimal thermal performance in systems utilizing CXL technology.

Deploying CXL Type 2 for Accelerator Integration and Memory Expansion

Deploying CXL Type 2 enables you to connect accelerators seamlessly and expand memory flexibly to meet your performance needs. With optimized data transfer speeds, you can guarantee efficient communication between components. This approach provides a versatile solution for enhancing system performance and scalability.

Seamless Accelerator Connectivity

To achieve seamless accelerator connectivity, leveraging CXL Type 2 technology allows for direct, high-speed communication between accelerators and host systems. This integration guarantees efficient access to the memory hierarchy while maintaining cache coherence, critical for performance. Key benefits include:

- Reduced latency by enabling direct memory access

- Simplified data sharing across devices

- Improved cache management between host and accelerators

- Enhanced scalability for multiple accelerators

With CXL Type 2, accelerators can access memory resources transparently, minimizing bottlenecks. This setup promotes a unified memory environment, optimizing workload distribution. By ensuring cache coherence, data consistency stays intact across the system. This approach simplifies system design and boosts performance, making it easier to deploy accelerators seamlessly within existing architectures. Additionally, vetted knowledge about cookie management and user privacy can help ensure that such advanced integrations respect user consent and data security standards. Implementing standardized protocols further ensures compatibility and reliable operation across diverse hardware components.

Flexible Memory Expansion Options

Leveraging CXL Type 2 technology enables flexible memory expansion by allowing systems to seamlessly add or reconfigure memory resources as needed. This flexibility depends on broad hardware compatibility, ensuring that various memory modules and accelerators work together smoothly. When deploying CXL Type 2 devices, you need to contemplate firmware updates, which are essential for maintaining compatibility and unlocking new features. Firmware updates help optimize system stability and performance as hardware evolves, preventing potential bottlenecks. With CXL Type 2, you can expand memory capacity or reallocate resources dynamically, enhancing your system’s adaptability. Reliable hardware compatibility is crucial to ensure smooth integration and operation. By choosing compatible hardware and keeping firmware current, you guarantee reliable operation and maximize the benefits of flexible memory expansion through CXL technology. Additionally, understanding hardware standards is vital for ensuring future-proof deployments and maximizing investment longevity. Developing a clear understanding of system interoperability can further enhance your deployment strategy and long-term success. For example, future-proofing ensures your system remains adaptable as new hardware and standards emerge. Moreover, maintaining updated firmware across components can help prevent compatibility issues and improve overall system robustness.

Optimized Data Transfer Speeds

Implementing CXL Type 2 technology substantially enhances data transfer speeds, making it ideal for seamlessly integrating accelerators and expanding memory. This guarantees faster, more efficient communication while maintaining cache coherence across devices. To maximize benefits, focus on these key points:

- Leverages high-bandwidth links for rapid data exchange

- Maintains cache coherence, reducing latency and data inconsistencies

- Improves power efficiency by optimized data routing

- Enables scalable memory and accelerator integration without bottlenecks

- Supports digital vaults of comprehensive data, ensuring secure and reliable information sharing. Additionally, adopting these advanced protocols facilitates interoperability among diverse hardware components, promoting a cohesive system architecture. Emphasizing standardized protocols helps ensure consistent performance across different implementations.

Scaling With CXL Type 3: Large Memory Pools for High-Performance Computing

CXL Type 3 enables the creation of large, shared memory pools that are essential for high-performance computing workloads. With memory pooling, you can aggregate vast amounts of memory across multiple devices, reducing bottlenecks and improving efficiency. This flexibility allows you to tailor the hardware topology to optimize data access and minimize latency. Instead of separate memory modules, you can dynamically allocate resources based on workload demands, enhancing scalability. By leveraging CXL Type 3, you can build a cohesive memory infrastructure that adapts as your needs grow, ensuring high throughput and low latency. This approach simplifies managing complex hardware topologies, making your system more versatile and capable of handling demanding HPC tasks effectively.

Ensuring Compatibility and Interoperability Among CXL Devices

As you expand memory pools with CXL Type 3, ensuring compatibility and interoperability among different CXL devices becomes increasingly important. To achieve this, focus on:

- Standardizing device interfaces to reduce issues caused by device-specific protocols.

- Implementing uniform memory access methods to minimize memory latency variations.

- Verifying support for common CXL specifications across all devices involved.

- Maintaining firmware and driver updates that promote seamless communication between diverse hardware.

Latency and Bandwidth: What You Need to Know About CXL Types

Understanding the differences in latency and bandwidth among CXL Types is essential for optimizing system performance. CXL Type 1 offers low latency and dedicated memory bandwidth, ideal for tight coupling between CPU and memory devices. Type 2 provides shared memory resources with moderate latency, enabling flexible memory pooling. Type 3 delivers the highest memory bandwidth, connecting devices via a physical PCIe switch, but with increased latency. To maximize performance, focus on latency optimization by selecting the appropriate CXL type based on your workload’s sensitivity. For latency-critical applications, Type 1 is preferable, while Type 3 suits high-bandwidth needs. Recognizing these variations helps you balance memory bandwidth and latency, ensuring your system operates efficiently without bottlenecks. This understanding is key to leveraging CXL’s full potential.

Securing Memory Sharing: Data Integrity and Privacy in CXL Systems

Securing memory sharing in CXL systems is vital to protect data integrity and privacy as multiple devices access shared resources. To achieve this, encryption protocols are essential—they safeguard data both at rest and in transit. Proper power management ensures devices operate securely without exposing vulnerabilities during idle or low-power states. Key points to consider include:

- Implement robust encryption protocols for data confidentiality.

- Use hardware-based encryption for faster, secure processing.

- Manage power states carefully to prevent data leaks during transitions.

- Regularly update security policies to adapt to emerging threats.

Challenges and Limitations When Implementing CXL in Your System

Implementing CXL in your system introduces a range of challenges and limitations that can impact performance, security, and compatibility. Memory fragmentation becomes a concern as dynamic sharing and allocation across devices may lead to inefficient utilization and increased latency. Managing this fragmentation requires careful system design. Additionally, firmware updates are critical for maintaining CXL compatibility and security; however, they can be complex and disruptive, risking system stability if not handled properly. Compatibility issues might also arise with existing hardware or software, requiring careful integration and testing. These factors can hinder deployment, increase complexity, and demand ongoing maintenance. Addressing these challenges upfront guarantees a smoother implementation and helps access the full potential of CXL’s memory sharing capabilities.

Future Trends: How CXL Will Evolve in Next-Gen Hardware

As next-generation hardware develops, you’ll see CXL’s bandwidth capabilities expand considerably, enabling faster data transfer. Improved interoperability standards will make it easier to integrate CXL across diverse systems and components. These trends will shape how you design and optimize future hardware architectures for maximum performance.

Increased Bandwidth Capabilities

Future advancements in CXL are poised to dramatically boost bandwidth capabilities, enabling faster data transfer between CPUs, memory, and accelerators. This evolution will reduce memory latency and improve bandwidth efficiency, *unleashing* new performance levels. To achieve this, next-gen CXL will likely feature:

- Higher data transfer rates, increasing overall throughput

- Enhanced protocol optimizations for better bandwidth utilization

- Wider lanes for more simultaneous data streams

- smarter compression techniques to maximize existing bandwidth

These improvements will allow you to handle larger datasets with minimal latency, ensuring smoother operation of memory and accelerators. As bandwidth increases, you’ll experience more efficient resource sharing and faster computation, paving the way for more powerful and responsive hardware architectures in the future.

Enhanced Interoperability Standards

How will next-generation CXL standards enhance interoperability across diverse hardware components? They’ll leverage advanced concepts like quantum entanglement to enable real-time, secure communication between devices, reducing latency and synchronization issues. This approach allows components from different vendors and architectures to work seamlessly, similar to blockchain consensus mechanisms that ensure agreement across distributed systems. By adopting standardized protocols inspired by these technologies, CXL will facilitate smoother integration of CPUs, memory, accelerators, and future hardware. Enhanced interoperability will also support dynamic resource sharing, making systems more flexible and scalable. As a result, hardware components will communicate more reliably, regardless of their origins, paving the way for next-gen data centers and AI infrastructure that are faster, more adaptable, and easier to upgrade.

Planning Your CXL-Enabled Architecture: Tips for System Architects

Planning a CXL-enabled architecture requires careful consideration of your system’s specific needs and future growth. To optimize performance, focus on how CXL impacts your memory hierarchy and cache coherence. Here are key tips:

- Map your memory hierarchy to ensure efficient data flow and reduce latency.

- Design for cache coherence across devices to maintain data consistency.

- Assess workload demands to determine the appropriate CXL types (1, 2, or 3).

- Confirm your motherboard and system interfaces support CXL standards for seamless integration.

Troubleshooting Common Issues With CXL Memory Sharing

When encountering issues with CXL memory sharing, it’s essential to systematically identify the root cause to resolve them efficiently. Start by checking for increased memory latency, which can slow down data access and impact performance. If latency spikes, verify the CXL topology and ensure proper configuration of switches and endpoints. Errors during data transfer might signal issues with error correction mechanisms; ensure error correction is enabled and functioning correctly on all devices. Firmware mismatches or outdated drivers can also cause communication problems, so keep your firmware and software up to date. Additionally, review system logs for warnings or errors related to memory sharing. Addressing these areas methodically helps you troubleshoot effectively and maintain ideal CXL memory sharing performance.

Real-World Examples: How Organizations Use CXL Today

Organizations are leveraging CXL today to optimize data centers by enabling faster resource sharing and improved scalability. AI accelerators benefit from CXL’s high-speed connections, allowing seamless integration with existing systems. In high-performance computing, CXL helps manage massive data loads more efficiently, boosting overall system performance.

Data Center Optimization

Curious about how data centers are maximizing performance and efficiency today? Many leverage CXL to optimize their memory hierarchy and enhance data security. By integrating CXL, organizations can:

- Increase memory pooling, reducing latency and boosting throughput.

- Enable dynamic resource allocation, adapting quickly to workload demands.

- Improve data security through hardware-level isolation and protection.

- Simplify architecture, lowering costs and boosting scalability.

These strategies allow data centers to handle diverse workloads more effectively. CXL’s ability to share memory resources across devices minimizes bottlenecks and supports real-time data processing. Additionally, maintaining a robust memory hierarchy ensures faster access and better data security. Overall, CXL helps organizations achieve higher efficiency, flexibility, and security in their data center operations.

AI Accelerator Sharing

By leveraging CXL to optimize memory hierarchies, data centers are now better equipped to share AI accelerators across multiple workloads. This flexibility allows organizations to maximize resource utilization, reducing costs and increasing efficiency. CXL enables seamless access to AI accelerators, even when they’re integrated into different servers or modules, thanks to its support for diverse memory hierarchies. You’ll find that software compatibility becomes less of a hurdle, as CXL standards ensure that existing AI frameworks and tools can adapt easily. This real-world application means you can allocate AI acceleration dynamically, improving performance without sacrificing stability or compatibility. Overall, organizations benefit from streamlined resource sharing, better scalability, and more agile AI deployment strategies.

High-Performance Computing

How are leading data centers and research institutions leveraging CXL today to enhance high-performance computing? They’re using CXL to enable faster, more flexible memory sharing, which boosts overall system performance while maintaining memory security. This approach reduces latency and improves energy efficiency, crucial for demanding workloads. Key strategies include:

- Connecting multiple accelerators directly to CPUs for seamless data exchange

- Sharing memory pools across nodes to maximize resource utilization

- Implementing secure memory access to protect sensitive data

- Reducing power consumption through efficient memory management

Making the Decision: Which CXL Type Is Best for Your Needs?

Choosing the right CXL type depends on your specific needs and system requirements. If you prioritize flexibility and dynamic resource sharing, CXL Type 3 offers direct memory expansion but comes with higher CXL cost and complexity. For simpler setups focused on memory pooling, CXL Type 2 provides a good balance, offering fast access with moderate security considerations. If security is your top concern, especially in multi-tenant environments, CXL Type 1 ensures isolated communication and better CXL security. Your decision should weigh the importance of performance, scalability, cost, and security. Consider your workload demands and budget constraints carefully. Ultimately, selecting the appropriate CXL type aligns with your infrastructure goals, optimizing both performance and security while managing costs effectively.

Impact of CXL on High-Performance Computing and AI Workloads

CXL technology is transforming high-performance computing (HPC) and AI workloads by enabling faster, more efficient data transfer between processors, memory, and accelerators. This boosts overall system performance and reduces latency. Key impacts include:

- Improved scalability for large AI models and simulations.

- Enhanced data security through quantum encryption integration.

- Streamlined blockchain processes with rapid, reliable memory sharing.

- Reduced bottlenecks, allowing real-time analytics and faster training cycles.

These advancements facilitate more complex computations and secure data handling. As CXL evolves, it will support even more sophisticated HPC and AI applications, making systems more adaptable and resilient. The combination of memory sharing and emerging technologies like quantum encryption opens new possibilities for data integrity and privacy in high-stakes environments.

Summary: Choosing the Right CXL Type to Power Your Systems

Selecting the appropriate CXL type for your system depends on your specific performance needs and workload characteristics. If you require flexible memory virtualization and dynamic sharing, CXL Type 1 offers a good solution by connecting memory devices directly to CPUs. For more integrated memory expansion, Type 2 provides high bandwidth with direct memory sharing, but verify your hardware is compatible to avoid compatibility issues. If your goal is high-speed, high-capacity memory pooling for demanding applications like AI or HPC, Type 3 enables memory expansion over PCIe, but it demands careful hardware compatibility checks. Understanding your workload’s demands and verifying hardware compatibility will guide you in choosing the right CXL type, guaranteeing optimal performance, scalability, and efficient memory virtualization for your systems.

Frequently Asked Questions

How Does CXL Impact System Power Consumption and Energy Efficiency?

CXL improves your system’s power efficiency by enabling direct memory sharing and reducing data movement, which cuts down energy consumption. By optimizing resource allocation and allowing faster communication between devices, CXL helps you achieve energy savings. This efficient data handling means less power is wasted, resulting in a more energy-efficient system overall. So, adopting CXL can markedly lower your system’s power consumption while enhancing performance.

Can CXL Be Integrated With Existing Pcie-Based Infrastructure Seamlessly?

They say, “Old habits die hard,” but integrating CXL with existing PCIe infrastructure can be smooth if you address compatibility challenges early. While some adapters may need updates, many CXL devices are designed for seamless integration, enabling performance optimization without major overhauls. You might face hurdles, but with careful planning and the right hardware, you’ll find that CXL can enhance your system’s capabilities efficiently.

What Are the Security Risks Associated With CXL Memory Sharing?

You should be aware that CXL memory sharing can introduce security risks like compromised memory isolation and data confidentiality breaches. Since shared memory areas are accessible across devices, malicious actors could exploit vulnerabilities to access sensitive data or interfere with system operations. To mitigate these risks, guarantee strong access controls, encryption, and robust memory management practices are in place to protect data integrity and confidentiality within your system.

How Does CXL Handle Fault Tolerance and Error Recovery?

CXL handles fault tolerance by actively performing fault detection and error correction. When it spots a fault, it isolates the faulty memory segment to prevent data corruption. Error correction mechanisms automatically fix minor issues, while more serious faults prompt alerts or system resets. This approach guarantees data integrity and system stability, allowing you to maintain reliable memory sharing even amidst faults or errors.

Are There Industry Standards or Certifications for CXL Device Interoperability?

While industry standards and certification programs aim to guarantee CXL device interoperability, they’re still evolving, like a roadmap in progress. You’ll find that organizations are working on establishing clear guidelines to promote seamless integration. Certification helps verify compliance, giving you confidence in compatibility. As the ecosystem matures, expect more formal standards to emerge, simplifying your choices and ensuring your CXL devices work smoothly across different platforms.

Conclusion

Choosing the right CXL type is like finding the perfect key to unlock your system’s full potential. Whether you need quick device memory sharing or extensive hardware integration, understanding each type’s strengths helps you make informed decisions. As CXL continues to evolve, staying ahead means selecting the option that best fits your high-performance goals. Embrace this technology’s power—your system’s future depends on unlocking its full potential today.